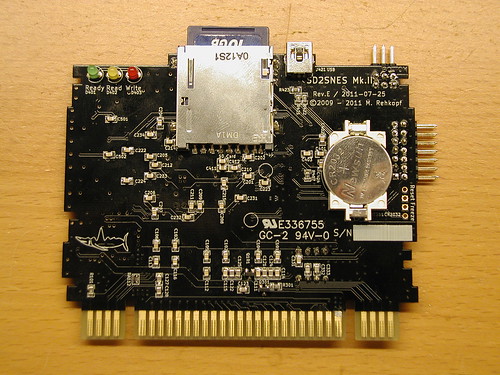

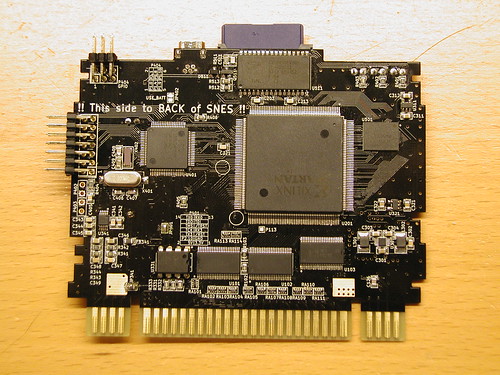

Prototype – assembled

I had the Rev.E proto assembled by the end of August – but never got around to showing it off. 😉

Well, here it is.

The fat 4MBit SRAM at the top isn’t used yet. Its purpose is to retain save data in case of power failure (before it’s written to SD card), to serve as custom chip work RAM, and probably to store some other status information. Save data is currently stored in PSRAM along with the ROM, and monitored/saved to card from there.

Though the Zeroplus Logic Cube is rather low-end, it’s still a 200MHz, 128kSamples LA that has proven invaluable for all sorts of debugging. The JTAG/UART adapter (not shown) is a run-of-the-mill FT2232 DIP adapter board which plays nicely with OpenOCD. This one I got cheap from Akihabara (thanks to Tobias Diedrich!).