A small recap, part 1

Development of sd2snes began in April 2009, inspired by sd2iec (hence the name).

Since 2001 I had been tinkering around with modified SNES cartridges, removing the ROMs to replace them with small self-made flash modules (usually a 29F032 or 29LV640 soldered on a small PCB with a pin header). They looked like this:

Even back then the idea to make a complete flash based cartridge from scratch was lingering in the back of my head. But it seemed too difficult to do for me. It also seemed impossible to implement new features, like additional memory maps, custom chips, etc. afterwards with the flexibility I wanted.

Fast forward to 2009. With time, more powerful yet affordable FPGAs had become readily available. Also sd2iec was released which provided ready-made SD card support (SPI mode).

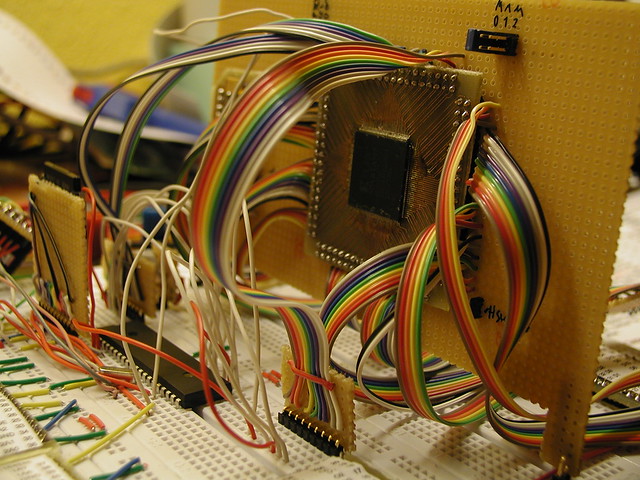

The first prototype was constructed on breadboard with lots of self made adapters, most notably the FPGA->breadboard adapter, with on board power supply and configuration jumpers.

Hardware specs of the breadboard were:

- Spartan3 FPGA, 144 pins

- ATMega644 MCU @12MHz (64kB flash, 4kB RAM)

- 16MBits of SRAM

- SPI SD interface, max. ~1.5MB/s (read)

- FPGA is configured by the MCU, loading a bit file from SD Card

- Placeholder for original CIC (lockout chip), only one region possible without modding the console

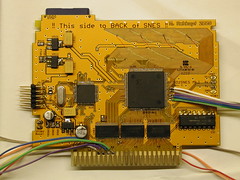

This design was more or less adapted for the first PCB prototypes (all of Mk.I), the only difference being more SRAM (64MBits). Loading was somewhat slow due to SPI mode and a maximum 6MHz SPI clock from the AVR. Later the FPGA was used to load blocks to RAM directly, increasing the read speed to ~1.5MB/s. SNES master clock (Pin 1) was used as a clock source for the FPGA. It proved unreliable (the DCM just stopped working at random) so in later revisions (and all of Mk.II) the AVR clock output was used to clock the FPGA. This resulted in the last revision of Mk.I having the additional groups of slot pins removed entirely.

Coming up: SuperCIC, MSU1, timing perils